DOI: 10.1002/asia.201300505

# Substrate Engineering by Hexagonal Boron Nitride/SiO<sub>2</sub> for Hysteresis-Free Graphene FETs and Large-Scale Graphene p-n Junctions\*\*

Hua Xu,[a, b] Juanxia Wu,[a] Yabin Chen,[a] Haoli Zhang,[b] and Jin Zhang\*[a]

Abstract: We have explored an approach for the fabrication of intrinsic and hysteresis-free graphene fieldeffect transistors (FETs) and for the construction of graphene p-n junctions based on substrate engineering by hexagonal boron nitride (h-BN)/SiO<sub>2</sub>. The effect of various interfaces on the performance of the graphene FETs was systematically studied by constructing four types of graphene devices (gragraphene/h-BN phene/SiO<sub>2</sub> FETs, FETs, h-BN/graphene/SiO2 FETs, and h-BN/graphene/h-BN FETs). Graphene/SiO<sub>2</sub> FETs and h-BN/graphene/ SiO<sub>2</sub> FETs always exhibit large hysteresis before and after annealing, whereas graphene/h-BN FETs and h-BN/graphene/h-BN FETs show intrinsic properties after annealing. Raman measurements also indicate that graphene on a SiO<sub>2</sub> substrate contains large amounts of p-doping, whereas that on a h-BN substrate is intrinsic. Thus, the graphene/h-BN interface gives intrinsic and hysteresis-free graphene FETs, whilst the graphene/SiO<sub>2</sub> interface affords p-doping and a hysteresis effect in the graphene FETs. This result is because h-BN serves as an insulation layer, which prevents charge trapping

**Keywords:** boron nitride • hysteresis • field-effect transistors • graphene • substrate engineering

between the graphene and the charge traps at the graphene/SiO<sub>2</sub> interface, which cause the hysteresis. In addition, the negligible electrostatic doping of h-BN into graphene also ensures the intrinsic and hysteresis-free properties of graphene/BN/SiO<sub>2</sub> FETs. Moreover, benefitting from the p-doped and intrinsic features of graphene on SiO2 and h-BN substrates, respectively, large-scale graphene p-n junction superlattices with great potential difference are constructed and integrated into photodetector arrays by substrate engineering with h-BN/SiO<sub>2</sub>. Efficient hot carrier-assisted photocurrent was generated by laser excitation at the junction under ambient conditions.

# Introduction

Since its discovery in 2004,<sup>[1]</sup> graphene has been considered to be the most-promising candidate for next-generation electronic devices, owing to its superior electrical properties and unique 2D structure.<sup>[2]</sup> Graphene-based field-effect transistors (FETs) show exceptional carrier density and polarity tunability, high current densities, as well as extraordinarily high mobility for both electrons and holes.<sup>[3]</sup> However, the nature of graphene, a one-atom thick carbon membrane in which every atom is exposed to the external environment,

[a] Dr. H. Xu, J. Wu, Y. Chen, Prof. J. Zhang Center for Nanochemistry

College of Chemistry and Molecular Engineering Peking University

Beijing 100871 (China)

Fax: (+86)01062752555

E-mail: jinzhang@pku.edu.cn

[b] Dr. H. Xu, H. Zhang State Key Laboratory of Applied Organic Chemistry College of Chemistry and Chemical Engineering Lanzhou University Lanzhou 730000 (China)

[\*\*] FET=Field-effect transistor.

Supporting information for this article is available on the WWW under http://dx.doi.org/10.1002/asia.201300505.

makes it highly sensitive towards its local surroundings, such as substrate curvature<sup>[4]</sup> and charge traps at interfaces.<sup>[5,6]</sup> This high sensitivity causes the graphene-based FETs to exhibit low carrier mobility, heavy doping, and, in particular, a large hysteresis effect when measured under ambient conditions.<sup>[7-9]</sup> In particular, the field-effect properties show dependence on the measurement parameters and environmental variation, which hampers the accurate assessment of the performance of graphene FETs.[7,10,11] In spite of some efforts towards the development of more intrinsic and highcarrier-mobility graphene FETs,[3,12,13] several challenges remain. For example, the preparation of suspended graphene devices requires a number of complex fabrication steps and is usually expensive, which is unsuitable for largescale technological applications. Moreover, modifying the substrate with organic molecules is limited by the stability of molecules and vacuum annealing is difficult to perform experimentally; thus, an even-larger p-doping and hysteresis effect will arise after re-exposing the device to ambient air. [4,10,13] Therefore, it is critical to develop an effective and reliable method for suppressing the doping and hysteresis effects for the future application of graphene FETs.

According to a previous study, the charge trapping/detrapping between graphene and charge traps at a graphene/SiO<sub>2</sub> interface causes the doping and hysteresis effects in graphene FETs.<sup>[9,10,14]</sup> Thus, the introduction of a stable insulation layer that can suppress such charge trapping/detrapping

2446

should be an effective way of suppressing the hysteresis effect. Hexagonal boron nitride (h-BN) is a promising material as a substrate for graphene devices, because of its hydrophobicity, atomically smooth surface, large electrical bandgap, low dielectric constant (about 4), chemical inertness, etc. [3,15] As such, the combination of graphene and h-BN has attracted great attention because it has potential to open up the exciting possibility of creating a new class of graphenebased electronic devices.[16-18] Previous work has shown that the mobility and the local electronic properties of graphene can be greatly improved when deposited onto a h-BN substrate, owing to its ultra-flat surface. [15,17] h-BN has also been used as a dielectric layer for graphene devices.<sup>[19]</sup> In addition, theory predicts that a band-gap can be opened up in graphene if it is sandwiched between two h-BN films.<sup>[20]</sup> In particular, h-BN can be used as a barrier layer in BN/graphene/BN multilayered heterostructures for electron tunneling between two graphene layers and for graphene-based vertical tunneling transistors.<sup>[18]</sup> So, to reveal whether electrostatic doping exists at the graphene/BN interface, it is also critical to study combined graphene and h-BN electronic devices.

Herein, we have systematically studied the effect of different interfaces (graphene/SiO<sub>2</sub>, graphene/h-BN/SiO<sub>2</sub>, h-BN/graphene/SiO<sub>2</sub>, and h-BN/graphene/h-BN) on the performance of graphene FETs to explore the way of suppressing the doping and hysteresis in graphene FETs (Figure 1). Electrical and Raman properties show that the graphene/SiO<sub>2</sub> interface introduces p-doping and hysteresis effects into graphene FETs, whilst the graphene/BN interface gives intrinsic and hysteresis-free graphene FETs. These results indicate that charge trapping/detrapping of graphene with charge traps from the graphene/SiO<sub>2</sub> interface, which cause the hysteresis, can be effectively blocked by insulating with a h-BN layer. Furthermore, a large-scale and periodic graphene p-n junction was constructed through BN/SiO<sub>2</sub> substrate engineering, which is beneficial for the integration of

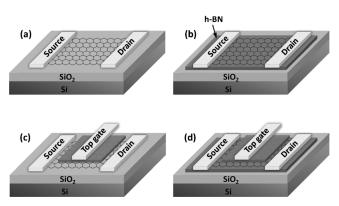

Figure 1. Schematic representation of four types of graphene FETs: a) Graphene on a SiO<sub>2</sub> substrate forms typical graphene/SiO<sub>2</sub> FETs; b) graphene on a h-BN substrate forms graphene/BN/SiO<sub>2</sub> FETs; c) graphene sandwiched between SiO<sub>2</sub> and h-BN substrates forms BN/graphene/SiO<sub>2</sub> FETs; and d) graphene sandwiched between two h-BN substrates forms BN/graphene/BN FETs.

large-scale graphene-based optoelectronic devices for future applications.

# Results and Discussion

First, we focused on the electrical field-effect properties of graphene/SiO<sub>2</sub> FETs (that is, a graphene-based device that was fabricated on a SiO<sub>2</sub> substrate). Figure 2a shows a plot

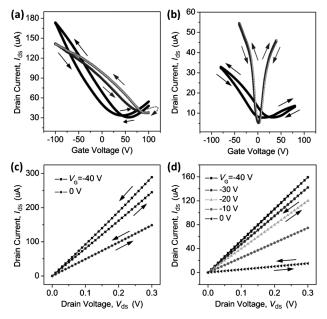

Figure 2. Representative transfer curves of a) graphene/SiO $_2$  FETs and b) graphene/BN/SiO $_2$  FETs before (black) and after annealing (gray). The back-gate voltage,  $V_{\rm B-G}$ , is swept from  $-100~\rm V$  to  $+100~\rm V$  and then back to  $-100~\rm V$  at a rate of  $0.1~\rm V\,s^{-1}$ . Output curves of c) graphene/SiO $_2$  FETs and d) graphene/BN/SiO $_2$  FETs after annealing. The drain voltage,  $V_{\rm ds}$  is reversibly swept from  $0~\rm V$  to  $0.3~\rm V$  under different  $V_{\rm B-G}$  values. The arrows in (a,b) and (c,d) denote the directions of the  $V_{\rm B-G}$  and  $V_{\rm ds}$  sweeps, respectively.

of the source-drain current  $(I_{ds})$  as a function of the reverse back-gate voltage  $(V_{\rm B-G})$  that was applied to the silicon back gate of the graphene/SiO2 FETs before and after annealing in a H<sub>2</sub>/Ar flow at 350 °C for 3 h. The transfer curves that were recorded during the up and down sweeps of  $V_{\rm R-G}$ of graphene before annealing showed poor reproducibility and each curve showed asymmetry between the electron and hole doping. The gate voltage that corresponded to the charge-neutral point  $(V_{\rm Dirac})$  for these two curves showed a large splitting ( $\Delta V_{\rm Dirac} = 30 \text{ V}$ ). In addition, the output curves of graphene/SiO $_2$  FETs with  $V_{\rm ds}$  reversible sweeping between 0 V and 0.3 V showed very good reversibility at  $V_{\rm B-G}$  = 0 V, whereas they showed clear splitting at  $V_{\rm B-G}$  > 0 V, as shown in Figure 2c. All of these phenomena indicate that the graphene device that is fabricated on a SiO<sub>2</sub> substrate has large p-doping and hysteresis effects. The origin of the p-doping and the gate hysteresis in graphene/SiO<sub>2</sub> FETs, which has long been studied but remains disputed, is

usually attributed to the charge trapping of graphene by the charge traps of  $\rm H_2O/O_2$  molecules,  $^{[4,9,10]}$  the  $\rm SiO_2$  dielectric layer,  $^{[5]}$  photoresist residues, or other contaminants. Furthermore, heavy p-doping and a large gate hysteresis arise in graphene/SiO<sub>2</sub> FETs after annealing and the  $V_{\rm Dirac}$  for these two curves shifts to more-positive values such that are even outside of our  $V_{\rm B-G}$  sweep range. This phenomenon is usually observed in traditional graphene/SiO<sub>2</sub> FETs, although the reason for it is still debated. The carrier mobility was calculated from the linear regime of the transfer characteristics according to Equation (1), where  $C_{\rm g}$  is the gate capacitance of the dielectric materials,  $I_{\rm ds}$  is the drain current,  $V_{\rm G}$  is the gate voltage, and  $\mu_{\rm FET}$  is the field-effect mobility.  $^{[5]}$

$$\mu_{\rm FET} = \frac{L}{C_{\rm g}WV_{\rm d}}\frac{dI_{\rm d}}{dV_{\rm G}} = g_{\rm m}\frac{L}{V_{\rm d}WC_{\rm g}} \eqno(1)$$

$\rm d\emph{I}_d/d\emph{V}_G$  was calculated from the slope to be between  $V_G\!=\!-40\,\rm V$  and  $V_{\rm Dirac}.$  The calculated hole-carrier mobility ( $\mu$ ) of graphene/SiO $_2$  FETs was only 5740 cm $^2\rm V^{-1}\rm s^{-1}$  at  $V_{\rm ds}\!=\!0.1\,\rm V;$  this low mobility is attributed to doping-induced scattering of the transport carriers in graphene.

In contrast, the electrical field-effect properties of graphene/BN FETs (that is, a graphene device that was fabricated on a h-BN substrate) were very different to those of graphene/SiO<sub>2</sub> FETs, as shown in Figure 2b. The transfer curves for graphene/BN/SiO2 FETs before annealing exhibited relatively small p-doping and gate hysteresis ( $\Delta V_{\rm Dirac}$ = 30 V), owing to the charge trapping/detrapping of graphene with charge traps (H<sub>2</sub>O/O<sub>2</sub>, residues, or others) that were introduced during the transfer process. However, the transfer curves under  $V_{\rm B-G}$  up and down sweeping showed extremely good reproducibility and the  $V_{\mathrm{Dirac}}$  of these two curves hardly changed (about 0 V) after annealing the device to remove the charge traps. The suppression of the hysteresis effect in graphene/h-BN FETs is also reflected in their output properties, as shown in Figure 2d; the output curves with  $V_{\rm ds}$  reversible sweeping between 0 V and 0.3 V show very good reversibility at all  $V_{\rm B-G}$  values. In particular, the carrier mobility of the graphene/BN/SiO2 FETs is greatly increased (28630 cm $^2$ V $^{-1}$ s $^{-1}$  at  $V_{\rm ds}$ =0.1 V), owing to the suppression of doping-induced scattering in graphene. Moreover, the electrical field-effect properties of graphene/h-BN FETs exhibit much-higher stability compared to graphene/ SiO<sub>2</sub> FETs, as shown in the Supporting Information, Figure S3. Herein, we have to emphasize that the two strict annealing processes, that is, annealing h-BN in air after being cleaved onto a SiO<sub>2</sub> substrate and annealing the graphene/h-BN complex after transfer, are very important for decreasing the contact resistance and increasing the carriers mobility of these devices, as shown in the Supporting Information, Figure S4.

To further clarify the effect of different interfaces on the properties of graphene FETs, we studied the field-effect properties of h-BN/graphene/SiO<sub>2</sub> FETs and h-BN/graphene/h-BN FETs. For h-BN/graphene/SiO<sub>2</sub> FETs, graphene/BN and graphene/SiO<sub>2</sub> interfaces were formed on the

top and bottom surfaces of graphene, receptively. As with graphene/SiO<sub>2</sub> FETs, the transfer curves of h-BN/graphene/SiO<sub>2</sub> FETs at the bottom gate exhibited large p-doping and gate hysteresis, as shown in Figure 3 a. This result should be

Figure 3. Representative transfer curves of BN/graphene/SiO $_2$  FETs under reversible a) bottom-gate ( $V_{\rm B-G}$  from  $-100~\rm V$  to  $+100~\rm V$ ) and b) top-gate sweeping ( $V_{\rm T-G}$  from  $-10~\rm V$  to  $10~\rm V$ ). Transfer curves of BN/graphene/BN FETs under reversible c) bottom-gate ( $V_{\rm B-G}$  from  $-40~\rm V$  to  $+40~\rm V$ ) and d) top-gate sweeping ( $V_{\rm T-G}$  from  $-4~\rm V$  to  $+4~\rm V$ ).  $V_{\rm ds}=0.1~\rm V$ . The arrows in these figures denote the sweep direction of the gate voltage. Both BN/graphene/SiO $_2$  FETs and BN/graphene/BN FETs were annealed at 350 °C for 2 h to remove the residues device fabrication before the electrical measurements.

due to the charge trapping/detrapping of graphene with charge traps from both dielectric SiO<sub>2</sub> and H<sub>2</sub>O/O<sub>2</sub> at the graphene/SiO<sub>2</sub> interface. Moreover, the transfer curves of this device at the top gate, with h-BN as a dielectric layer, also exhibited p-doping and hysteresis (Figure 3b). This result shows that the H<sub>2</sub>O/O<sub>2</sub> charge traps, which only exist at the graphene/SiO<sub>2</sub> interface, still cause the gate hysteresis in this top-gate device, because there is no electrostatic charge transfer at the graphene/h-BN interface (see below). Thus, just protecting the top surface with h-BN cannot suppress the doping and gate hysteresis because the charge traps come from the graphene/SiO<sub>2</sub> interface, rather than the graphene/air interface. For BN/graphene/BN FETs, two graphene/h-BN interfaces were formed on the top and bottom surfaces of graphene. As shown in Figure 3c,d, the p-doping and gate hysteresis were effectively suppressed at both the top and bottom gates, which indicates that there is no electrostatic charge transfer at the graphene/h-BN interface. This result is important for the use of h-BN as a dielectric or barrier layer for combined graphene and h-BN electronic devices.

From this above study of the effect of different interfaces on the performance of graphene FETs, we know that the

charge traps that cause p-doping and gate hysteresis in graphene/SiO<sub>2</sub> FETs mainly come from the graphene/SiO<sub>2</sub> interface. The introduction of a thin hydrophobic layer of h-BN as insulation between graphene and the SiO<sub>2</sub> substrate can block the charge trapping and, thus, suppress the p-doping and gate hysteresis. That is, for high-performance graphene FETs, there is the good (the h-BN substrate), the bad (the SiO<sub>2</sub> substrate), and the ugly (charge traps from the graphene/SiO<sub>2</sub> interface). However, this difference between graphene on h-BN and SiO<sub>2</sub> substrates is beneficial for constructing graphene heterojunctions.

Graphene heterojunctions are attracting great interest, owing to their potential use in the field of high-speed photodetectors, [21] photovoltaics, and thermoelectricity. [22] More recently, it has been shown that a graphene superlattice structure can lead to a number of fascinating new phenomena, including electron-beam supercollimation, anisotropic transmission, the creation of additional Dirac cones, and effective magnetic fields.<sup>[23]</sup> To date, most graphene heterojunctions have been fabricated by using multiple electrostatic gates, [24] electrical stress-induced doping, [25] chemical treatment by gas exposure, [10] chemical modifications on the top of graphene, [26] and modification of the substrate by self-assembled monolayers.<sup>[27]</sup> However, current methods for electrostatic gating require a number of fabrication steps, which may not be easily scalable on an industrial level and are usually expensive. Furthermore, chemical doping on the top of graphene can degrade the carrier mobility in the device through the introduction of defects and impurities into the graphene. In addition, physisorbed dopant molecules are not stable and may be desorbed, which would result in changes in the electronic properties of graphene. Thus, the development of a facile and scalable technique for the construction of graphene heterojunctions is needed.

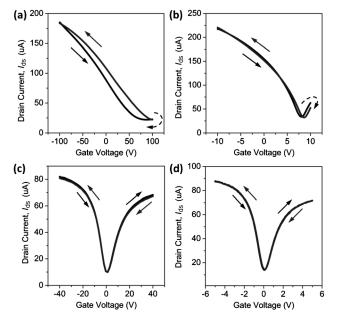

From these above results, we know that h-BN and SiO2 substrates afford intrinsic and pdoped graphene, respectively. Thus, there should be a potential difference between graphene on h-BN and SiO2 substrates when a graphene sheet is stretched across these two substrates, as shown in Figure 4a. Figure 4b shows an optical image and Raman features of graphene that has been deposited across h-BN and SiO<sub>2</sub> substrates; the dashed square denotes the area that was scanned for Raman imaging. The Raman mapping of the Gband frequency ( $\omega_G$ ), the 2Dband frequency  $(\omega_{2D})$ , and the intensity ratio of the 2D  $(I_{2D})$ and G bands  $(I_G)$ ,  $I_{2D}/I_G$ , which can be used to judge the doping

of graphene, [28] is shown in Figure 4b. This mapping reveals a remarkable  $\omega_G$  shift from about 1585 cm<sup>-1</sup> in the h-BN substrate area (middle section) to about 1595 cm<sup>-1</sup> in the SiO<sub>2</sub> substrate area (right section), thereby clearly indicating two distinct surfaces. In addition to an up-shift in  $\omega_G$  ( $\Delta\omega_G$  $\approx 10 \text{ cm}^{-1}$ ), an up-shift in  $\omega_{2D}$  ( $\Delta \omega_{2D} \approx 10 \text{ cm}^{-1}$ ) and a decrease in  $I_{\rm 2D}/I_{\rm G}$  on moving from the from h-BN area to the SiO<sub>2</sub> area are also seen. For a clearer comparison, the typical Raman spectra for the two spots on the graphene in the SiO<sub>2</sub> and h-BN regions are shown in Figure 4b, top right. The Raman spectrum of graphene on the SiO<sub>2</sub> substrate (right section) exhibits a typical p-doping effect on the spectroscopic characteristics of the G and 2D bands, whilst that on the h-BN substrate (middle section) not only shows typical spectroscopic characteristics of intrinsic graphene, but also an additional peak at 1367 cm<sup>-1</sup>, which is ascribed to the Raman signals of the underlying h-BN film. Thus, the observed up-shifts in  $\omega_{\rm G}$  and  $\omega_{\rm 2D}$  and the decrease in  $I_{\rm 2D}/I_{\rm G}$ of graphene on moving from the BN substrate region to the SiO<sub>2</sub> substrate region, which are attributed to the p-doping of graphene, indicate that a graphene p-n junction is formed at the boundary of the SiO2 and h-BN substrates. (In fact, it should be more accurately defined as a p-i junction, but herein we call it a p-n junction because it is homogeneously formed in the same graphene film.) The potential difference of the graphene p-n junction,  $\Delta E_{\rm F} = |E_{\rm F(SiO2)} - E_{\rm F(BN)}|$ , can be approximately calculated from the shift in the G-band frequency,  $\Delta\omega_{G}\!=\!\left.\left|\left.\omega_{G(SiO2)}\!-\!\omega_{G(BN)}\right.\right|\right.,$  according to Equation (2), where  $\langle D_T^2 \rangle_F = 45.6 \text{ eV}^2 \text{Å}^{-2}$  is the deformation potential of the  $E_{2g}$  mode, M is the atomic weight of carbon,  $\omega_0$  is the frequency of the G band in undoped graphene,  $v_F$ is the Fermi velocity of graphene, and  $\alpha' = 4.39 \times 10^{-3}$ . [29]

Figure 4. a) Schematic representation of the potential profile of a graphene p-n junction that was constructed by  $BN/SiO_2$  substrate engineering. b) Raman spectra and imaging of graphene that was stretched across BN and  $SiO_2$  substrates. Transfer curves of graphene that was stretched across the h-BN and  $SiO_2$  substrates c) before and d) after annealing.

$$\hbar\Delta\omega = \frac{\hbar A \langle D_F^2 \rangle_F}{\pi M \omega_0 (\hbar v_F)^2} |\epsilon_F| = \alpha' |\Delta E_F| \tag{2}$$

The corresponding carrier density can be expressed by  $\Delta n = \pi^{-1}(E_{\rm F}/\hbar v_{\rm F})^2$  ( $\hbar v_{\rm F} \approx 5~e$  Å). For a graphene p–n junction,  $\Delta \omega_{\rm G} \approx 10~{\rm cm}^{-1}$ , as calculated from the difference between the observed  $\omega_{\rm G(SiO2)} = 1595~{\rm cm}^{-1}$  and  $\omega_{\rm G(BN)} = 1585~{\rm cm}^{-1}$ , thus signifying a potential difference of  $\Delta E_{\rm F} \approx 0.250~{\rm eV}$ , which corresponds to a hole-carrier density of  $\Delta n \approx 1.25 \times 10^{13}~{\rm cm}^{-2}$ .

To investigate the electrical transport properties of this graphene p-n junction, we prepared a device in which the graphene channel was stretched across h-BN and SiO2 substrates. Figure 4c shows a transfer curve of FETs with a graphene p-n junction before annealing. We observed two different  $V_{\rm Dirac}$  points, at  $V_{\rm B-G} \approx 8~{\rm V}$  and  $V_{\rm B-G} \approx 48~{\rm V}$ , which corresponded to the  $V_{\rm Dirac}$  of graphene on h-BN and SiO<sub>2</sub> substrates, respectively. On the basis of the two separated  $V_{\rm Dirac}$ , three distinct regions in the  $I_{\rm ds}$ - $V_{\rm G}$  graph of the graphene p-n junction FETs can be identified as p+-p, p-n, and n-n<sup>+</sup> regions. Graphene on both SiO<sub>2</sub> and h-BN substrates are p-doped at  $V_{\rm B-G}$  < 8 V. Graphene on a SiO<sub>2</sub> substrate is p-doped, whereas graphene on a h-BN substrate is n-doped within the range  $V_{\rm B-G}$ =8-48 V. Graphene on both  $SiO_2$  and h-BN substrates are n-doped at  $V_{B-G} > 48$  V. The potential difference between the Dirac points, as revealed by the double  $V_{\rm Dirac}$ , clearly confirms the existence of a graphene p-n junction. The potential difference of a graphene p-n junction can also be approximately calculated from  $\Delta V_{\text{Dirac}} = |V_{\text{Dirac(SiO2)}} - V_{\text{Dirac(BN)}}|$ , according to Equations (3) and (4), where  $v_F = 10^6 \text{ m s}^{-1}$ , n,  $C_a$ , e, and  $V_{Dirac}$  are the Fermi velocity, charge density, gate capacitance, electron charge, and the gate voltage that corresponds to the charge-neutral Dirac point, respectively.[30]

$$E_{\rm F}(n) = -\operatorname{sgn}(n)\hbar v_{\rm F} \sqrt{(\pi|n|)} \tag{3}$$

$$n = \alpha V_{g} = C_{g}(V_{g} - V_{Dirac})/e \tag{4}$$

For the graphene p–n junction before annealing,  $\Delta V_{\rm Dirac} = |V_{\rm Dirac(BN)} - V_{\rm Dirac(SiO2)}| \approx 40~{\rm V}$  and the potential difference is  $\Delta E_{\rm F} \approx 0.196~{\rm eV}$ . Furthermore, after annealing the graphene p–n junction FETs, the  $V_{\rm Dirac(BN)}$  negatively shifts to about 0 V, whilst  $V_{\rm Dirac(SiO2)}$  positively shifts to about 75 V. These results correspond to our results in Figure 2 a, b, that is, that thermal annealing makes graphene on h-BN substrate more intrinsic, whilst it causes a large p-doping of graphene on a SiO<sub>2</sub> substrate. The value of  $\Delta V_{\rm Dirac}$  increases to about 75 V, thus signifying a potential difference of  $\Delta E_{\rm F} \approx 0.268~{\rm eV}$ , which matches well with the value that was calculated from  $\omega_{\rm G}$  ( $\Delta E_{\rm F} \approx 0.250~{\rm eV}$ ).

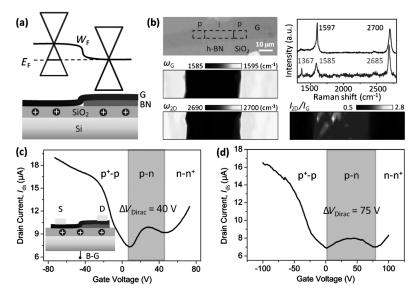

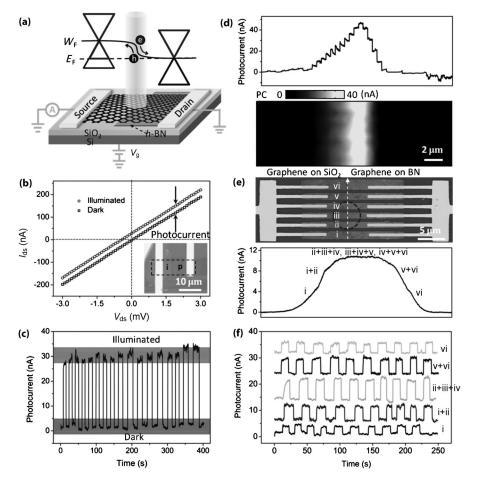

The remarkably large  $\Delta E_{\rm F}$  value of our graphene p-n junction facilitates the efficient generation of a photocurrent under illumination, based on the photothermoelectric (PTE) effect, as shown in Figure 5a. As a demonstration, one graphene p-n junction that had been constructed by substrate engineering with h-BN/SiO<sub>2</sub> was embedded into a two-terminal device (Figure 5b, inset). A focused 632.8 nm laser

spot (diameter≈2 μm, about 1 mW) was used to excite the photocarriers. As shown in Figure 4b, the p-n junction produced a pronounced current shift when illuminated by the laser, thus indicating its capability of photoelectric conversion. The photocurrent can be reversibly switched between "ON" and "OFF" states under dark and photo-illumination (Figure 5c). Thus, the reliability and stability of the photodetector were confirmed. We further conducted photocurrent mapping of the device (Figure 5d) and clearly observed that the photocurrent was generated over the junction, as well as the two electrodes, in contrary directions. Moreover, the intensity of the photocurrent that was generated at the junction (about 40 nA) was much higher than that at the graphene/electrodes junctions (about 4 nA), thus indicating a higher efficiency for potential photodetector applications. The gate-dependent photocurrent at the channel of the p-n junction device is significantly different to that at a sourceand-drain electrode (see the Supporting Information, Figure S4), which is consistent with photocurrent generation based on the PTE effect. Basis on this above analysis, the photocurrent response of a graphene p-n junction can be greatly improved by thermally annealing the device to enlarge the  $\Delta E_{\rm F}$  A photocurrent response of up to 0.125 mAW<sup>-1</sup> can be obtained for a device with a graphene p-i junction that was constructed by substrate engineering with h-BN/SiO<sub>2</sub> substrates after annealing at 350°C for 3 h (see the Supporting Information, Figure S5).

In addition to the advantage of easier preparation, another advantage of the construction of graphene p-n junctions by substrate engineering with BN/SiO<sub>2</sub> is its scalable production. Benefitting from recent progress in the chemical vapor deposition (CVD)-based growth of large-area graphene and h-BN films, [31] large-scale and periodic graphene p-n junctions of various morphologies can be constructed by substrate engineering with h-BN/SiO<sub>2</sub> (see the Supporting Information, Figures S6 and S7). Thus, we further studied the integration of multiple graphene photodetector channels (Figure 5e) by integrating the p-n junction superlattices into graphene photodetector arrays. A laser spot with a diameter of about 5 µm was shone over three p-n junction channels to produce photocarriers. On sweeping the laser spot from points (i) to (vi), we observed six terraces in the photocurrent-time plot, which corresponded to the positioning of the laser spot over single, double, and triple p-n junction channels. Photocurrent signals from individual channels, as well as their additions, are shown in Figure 5 f. Clearly, the photocurrent multiplied with the increasing number of p-n junction channels, thus confirming the possibility of forming integrated photodetector arrays based on substrate engineering with h-BN/SiO<sub>2</sub> for potential applications in photovoltaic and multiple-signal computing.

# **Conclusions**

In summary, we have systematically studied graphene/substrate interfaces for enhancing the performance of gra-

Figure 5. a) Schematic representation of the photocurrent generation of a graphene p-n junction that was constructed by BN/SiO<sub>2</sub> substrate engineering. b) Plot of current versus source-drain bias with (circles) and without a 632.8 nm laser beam (squares) that was focused on the p-n junction. The difference between the two curves represents the photocurrent. Inset shows the OM image of the device. c) Photoelectric response and d) photocurrent mapping (top: line mapping, bottom: area mapping) of the graphene p-n junction that was constructed by BN/SiO<sub>2</sub> substrate engineering. e) Top: False-colored SEM image of integrated graphene p-n photodetector arrays. Individual channels are labeled from i-vi, with sharing of the source and drain electrodes. The dashed circle represents the size and position of the laser spot. Bottom: Photocurrent line-mapping from i-vi. f) Photoelectric response of individual channels and their additions.

phene-based FETs by using substrate engineering with h-BN/SiO<sub>2</sub>. The h-BN/graphene interface gives intrinsic, hysteresis-free, and high-mobility graphene FETs, because there is no electrostatic charge trapping at the graphene/BN interface; in particular, the h-BN film can suppress the charge trapping at the graphene/SiO2 interface, which causes the poor performance of graphene/SiO2 FETs. The absence of charge trapping at the graphene/BN interface affords the opportunity for the fabrication of high-performance graphene FETs and more-complex BN/graphene/BN sandwichstructured electronic devices. Finally, by using the p-doping effect of graphene on a SiO2 substrate and the intrinsic features of graphene on a h-BN substrate, we constructed large-scale and periodic graphene p-n junctions by depositing graphene onto a patterned h-BN/SiO<sub>2</sub> substrate. The p-n junctions between two portions can be used for efficient photocurrent generation through the photothermoelectric effect. This approach provides an effective way to construct graphene-based superlattices with well-controlled widths and structures for future applications, such as in optoelectronic devices and electron-beam supercollimation.

# **Experimental Section**

Fabrication of Four Types of Graphene FFTs

Graphene was prepared by the mechanical exfoliation of Kish graphite onto a Si wafer that was coated with an oxide layer (SiO2, 300 nm); the formation of monolayer graphene was identified by optical microscopy (OM) and Raman spectroscopy. Relatively thick (10-30 nm) hexagonal-BN (h-BN) flakes were cleaved onto another substrate and then annealed at 500°C in air for 3 h to remove any residues. Optical imaging, Raman spectroscopy, and atomic force microscopy (AFM) showed that high-quality and ultra-flat h-BN flakes of various thickness had been obtained (see the Supporting Information, Figure S1). Graphene/SiO<sub>2</sub> FETs were prepared by using standard electron-beam lithography and lift-off techniques, as described in our previous work.[10] The electrodes were made of Cr/Au (5 nm:50 nm). Graphene/h-BN/SiO2 FETs were fabricated by using the following multistep procedure: First, a graphene flake was transferred onto the top of a h-BN flake by using the position-selective transfer technique. Second, the graphene/h-BN/SiO2 complex was annealed at 350°C for 3 h to remove the residues that were formed during the transfer process. Third, standard electron-beam lithography and lift-off techniques were used to fabricate the

contact electrodes onto the graphene. h-BN graphene/SiO2 FETs and h-BN/graphene/h-BN FETs were fabricated by using similar methods, but with a few differences. For h-BN/graphene/SiO2 FETs, a h-BN flake was transferred onto the top of graphene on the SiO<sub>2</sub> substrate. For h-BN/ graphene/h-BN FETs, two-step position-selective transfer was used: First, a graphene flake was transferred onto the top of a h-BN flake to form the graphene/BN structure; then, another h-BN flake was transferred onto the top of the graphene/BN complex to form the BN/graphene/BN sandwich structure. Besides the general bottom-gated graphene FETs, top-gated graphene FETs, with h-BN as the dielectric layer, were also constructed in the same device by adding a contact electrode onto the h-BN layer. The OM image of these four types graphene devices are shown in the Supporting Information, Figure S2. All of these samples were annealed under a H<sub>2</sub>/Ar atmosphere at 350 °C for 3 h after each transfer step, which was critical for improving the performance of graphene FETs, as discussed below.

Substrate Engineering Construct Graphene p-n Junction

Graphene was stretched across the BN and  $SiO_2$  substrates by using the position-selective transfer technique. The source and drain electrodes were contacted onto the graphene on the BN and  $SiO_2$  substrates, respec-

tively, which made the graphene channel stretch across the BN and  ${\rm SiO_2}$  substrates.

Raman, Electrical, and Photoelectrical Measurements

Raman spectra were recorded on a Horiba HR800 Raman system with a 514.5 nm laser at a grating of 600 lines  $\rm mm^{-1}$ . The incident laser beam was focused by a  $100\times\rm objective$  and the laser power on the samples was kept below 0.5 mW to avoid laser-induced heating. Electrical measurements were performed on a Keithley 4200 semiconductor analyzer. All of the measurements were performed at RT in ambient air.

# Acknowledgements

This work was supported by the NSFC (50972001, 20725307, and 50821061), the MOST (2011CB932601 and 2007CB936203), and the Fundamental Research Funds for the Central Universities. We thank Prof. J. Kong for providing the CVD-grown BN.

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, A. A. Firsov, *Science* 2004, 306, 666–669.

- [2] A. K. Geim, K. S. Novoselov, Nat. Mater. 2007, 6, 183-191.

- [3] M. Lafkioti, B. Krauss, T. Lohmann, U. Zschieschang, H. Klauk, K. v. Klitzing, J. H. Smet, *Nano Lett.* 2010, 10, 1149–1153.

- [4] S. Ryu, L. Liu, S. Berciaud, Y. J. Yu, H. T. Liu, P. Kim, G. W. Flynn, L. E. Brus, *Nano Lett.* **2010**, *10*, 4944–4951.

- [5] Z. H. Liu, A. A. Bol, W. Haensch, Nano Lett. 2011, 11, 523-528.

- [6] J. H. Chen, C. Jang, S. Adam, M. S. Fuhrer, E. D. Williams, M. Ishi-gami, *Nat. Phys.* 2008, 4, 377–381.

- [7] T. Lohmann, K. v. Klitzing, J. H. Smet, Nano Lett. 2009, 9, 1973– 1979.

- [8] a) H. Xu, L. M. Xie, H. L. Zhang, J. Zhang, ACS Nano 2011, 5,

8338-8344; b) H. Xu, Y. B. Chen, W. G. Xu, H. L. Zhang, J. Kong,

M. S. Dresselhaus, J. Zhang, Small 2011, 7, 2945-2952.

- [9] P. L. Levesque, S. S. Sabri, C. M. Aguirre, J. Guillemette, M. Siaj, P. Desjardins, T. Szkopek, R. Martel, *Nano Lett.* 2011, 11, 132–137.

- [10] H. Xu, Y. B. Chen, H. L. Zhang, J. Zhang, Small 2012, 8, 2833-2840.

- [11] H. Wang, Y. Wu, C. Cong, J. Shang, T. Yu, ACS Nano 2010, 4, 7221–7228.

- [12] X. Du, I. Skachko, A. Barker, E. Y. Andrei, *Nat. Nanotechnol.* 2008, 3, 491–495.

- [13] Z. G. Cheng, Q. Y. Zhou, C. X. Wang, Q. Li, C. Wang, Y. Fang, Nano Lett. 2011, 11, 767–771.

- [14] H. m. Wang, Y. H. Wu, C. X. Cong, J. Z. Shang, T. Yu, ACS Nano 2010, 4, 7221–7228.

- [15] J. Xue, J. Sanchez-Yamagishi, D. Bulmash, P. Jacquod, A. Deshpande, K. Watanabe, T. Taniguchi, P. Jarillo-Herrero, B. J. LeRoy, *Nat. Mater.* 2011, 10, 282–285.

- [16] L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, M. I. Katsnelson, L. Eaves, S. V. Morozov, A. S. Mayorov, N. M. R. Peres, A. H. C. Neto, J. Leist, A. K. Geim, L. A. Ponomarenko, K. S. Novoselov, *Nano Lett.* 2012, 12, 1707–1710.

- [17] C. R. Dean, A. F. Young, I. Meric, C. Lee, L. Wang, S. Sorgenfrei, K. Watanabe, T. Taniguchi, P. Kim, K. L. Shepard, J. Hone, *Nat. Nanotechnol.* 2010, 5, 722–726.

- [18] L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov, L. A. Ponomarenko, *Science* 2012, 335, 947–950.

- [19] K. K. Kim, A. Hsu, X. Jia, S. M. Kim, Y. Shi, M. Dresselhaus, T. Palacios, J. Kong, ACS Nano 2012, 6, 8583–8590.

- [20] a) J. Zhou, L. Wang, R. Qin, J. X. Zheng, W. N. Mei, P. A. Dowben, S. Nagase, Z. X. Gao, J. Lu, J. Phys. Chem. C 2011, 115, 25273– 25280; b) A. Ramasubramaniam, D. Naveh, E. Towe, Nano Lett. 2011, 11, 1070–1075.

- [21] T. Mueller, F. Xia, P. Avouris, Nat. Photonics 2010, 4, 297-301.

- [22] N. M. Gabor, J. C. W. Song, Q. Ma, N. L. Nair, T. Taychatanapat, K. Watanabe, T. Taniguchi, L. S. Levitov, P. Jarillo-Herrero, *Science* 2011, 334, 648–652.

- [23] W. G. Zhu, H. Chen, K. H. Bevan, Z. Y. Zhang, ACS Nano 2011, 5, 3707-3713.

- [24] R. V. Gorbachev, A. S. Mayorov, A. K. Savchenko, D. W. Horsell, F. Guinea, *Nano Lett.* **2008**, 8, 1995–1999.

- [25] G. Rao, M. Freitag, H. Y. Chiu, R. S. Sundaram, P. Avouris, ACS Nano 2011, 5, 5848–5854.

- [26] H. C. Cheng, R. J. Shiue, C. C. Tsai, W. H. Wang, Y. T. Chen, ACS Nano 2011, 5, 2051 – 2059.

- [27] J. Baltazar, H. Sojoudi, S. A. Paniagua, J. Kowalik, S. R. Marder, L. M. Tolbert, S. Graham, C. L. Henderson, J. Phys. Chem. C 2012, 116, 19095–19103.

- [28] A. Das, S. Pisana, B. Chakraborty, S. Piscanec, S. K. Saha, U. V. Waghmare, K. S. Novoselov, H. R. Krishnamurthy, A. K. Geim, A. C. Ferrari, A. K. Sood, *Nat. Nanotechnol.* 2008, 3, 210–215.

- [29] S. Pisana, M. Lazzeri, C. Casiraghi, K. S. Novoselov, A. K. Geim, A. C. Ferrari, F. Mauri, *Nat. Mater.* **2007**, *6*, 198–201.

- [30] J. Yan, Y. B. Zhang, P. Kim, A. Pinczuk, Phys. Rev. Lett. 2007, 98, 166802.

- [31] a) X. S. Li, W. W. Cai, J. An, S. Kim, J. Nah, D. X. Yang, R. Piner, A. Velamakanni, I. Jung, E. Tutuc, S. K. Banerjee, L. Colombo, R. S. Ruoff, *Science* 2009, 324, 1312–1314; b) K. K. Kim, A. Hsu, X. Jia, S. M. Kim, Y. Shi, M. Hofmann, D. Nezich, J. F. Rodriguez-Nieva, M. Dresselhaus, T. Palacios, J. Kong, *Nano Lett.* 2012, 12, 161–166.

Received: April 12, 2013 Published online: July 9, 2013